商机详情 -

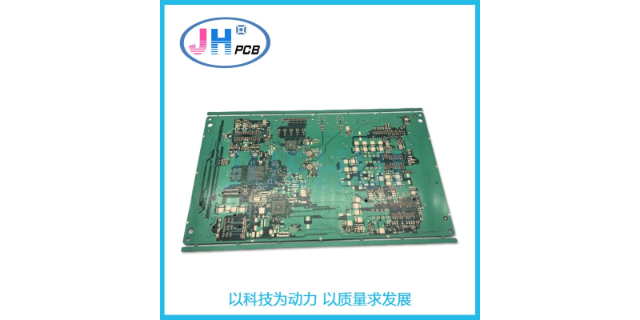

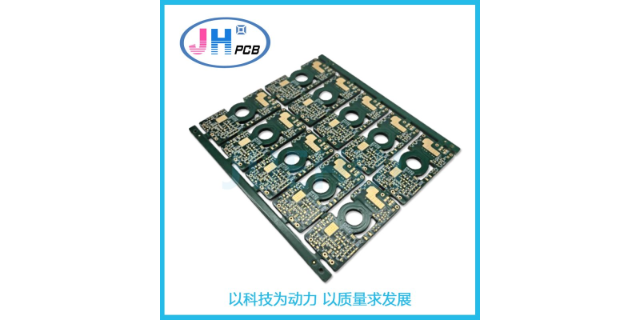

上海PCB贴片PCB电路板元器件

线路板沉金工艺是一种在铜层表面沉积镍和金的表面处理技术。一、抗氧化性沉金工艺形成的镍金层具有出色的抗氧化性能,能够有效防止铜层在潮湿、高温等恶劣环境下发生氧化,从而确保电路板的长期稳定性和可靠性。二、优异的焊接性能镍金层具有优异的可焊性,使得电子元器件与电路板之间的连接更加紧密可靠。这有助于提高焊接质量,降低焊接不良导致的故障率,从而确保电子设备的稳定运行。三、良好的导电性能金作为优良的导电材料,能够确保电路板的导电性能达到状态。这有助于提高电子设备的信号传输效率和稳定性,满足高性能、高可靠性的应用需求。线路板制造工厂的多样化生产类型。上海PCB贴片PCB电路板元器件

四层喷锡线路板布线的注意事项散热:四层喷锡线路板的布线应考虑元件的散热问题,避免元件过于集中导致散热不良。电磁兼容性:在布线时,应注意电磁兼容性问题,避免信号之间的干扰。可以采用屏蔽、滤波等技术来提高电路板的电磁兼容性。布线检查:在布线完成后,应进行布线检查,确保布线符合设计要求。可以使用布线检查软件来检查布线的连通性、间距、宽度等参数。四层喷锡线路板的布线规则和技巧对于提高电路板的性能和可靠性至关重要。在布线时,应根据电路板的具体要求和元件的特性,合理选择布线规则和技巧,以确保电路板的质量。湖南多层板PCB电路板定做PCB电路板短路了!怎样快速找到问题?

无铅喷锡是在PCB表面涂覆熔融锡铅焊料并用加热压缩空气整平(吹平)的工艺,使其形成一层既抗铜氧化又可提供良好的可焊性的涂覆层。热风整平时焊料和铜在结合处形成铜锡金属化合物,其厚度大约有1~2mil。PCB进行热风整平时要浸在熔融的焊料中,风刀在焊料凝固之前吹平液态焊料,并能够将铜面上焊料的弯月状小化和阻止焊料桥接。① HASL工艺的优点是:价格较低,焊接性能佳。② HASL工艺的缺点是:不适合用来焊接细间隙的引脚及过小的元器件,因为喷锡板的表面平整度较差,且在后续组装过程中容易产生锡珠(Solder bead),对细间隙引脚(Fine pitch)元器件较易造成短路。

沉锡由于所有焊料是以锡为基础的,所锡层能与任何类型的焊料相匹配,从这一点来看,沉锡工艺极具发展前景。但以前的PCB经沉锡工艺后易出现锡须,在焊接过程中锡须和锡迁移会带来可靠性问题,因此限制了沉锡工艺的采用。后在沉锡溶液中加入了有机添加剂,使锡层结构呈颗粒状结构,克服了之前的问题,而且还具有好的热稳定性和可焊性沉锡工艺可以形成平坦的铜锡金属间化合物,这个特性使得沉锡具有和热风整平一样的好的可焊性而没有热风整平令人头疼的平坦性问题;也没有化学镀镍/沉金金属间的扩散问题;只是沉锡板不可以存储太久。PCB线路板生产过程中对铜面氧化的防范策略。

加急PCB线路快板打样厂家需要投入更多的资源和人力。普通的PCB线路板订单通常需要一定的生产周期,以保证质量和效率。而加急订单则要求在短时间内完成,这就需要厂家调配更多的生产设备和工人,以满足客户的紧迫需求。为了能够及时交付加急订单,厂家需要增加生产线的运转速度,加大工作强度。其次,加急PCB线路快板打样厂家需要承担更高的风险。加急订单通常意味着时间紧迫,对于厂家来说,需要在短时间内完成设计、生产、检测等多个环节,这可能会增加出错的概率。一旦出现质量问题或延误交货,将会给客户带来不良影响,甚至损害厂家的声誉。因此,为了确保加急订单的质量和交货准时,厂家需要增加监控和质量控制措施,这也是收取加急费的原因之一。此外,加急PCB线路快板打样厂家还需要考虑资源利用的平衡。在一个厂家的生产线中,加急订单和普通订单需要共享有限的资源,如设备、人力和材料。如果过多地接受加急订单,将会导致普通订单的生产周期延长,从而影响其他客户的满意度和利益。为了维持生产线的平衡,厂家需要通过收取加急来进行资源的合理分配,保证每个订单都能得到适当的关注和处理。了解多层电路板偏孔的原因,提升生产效率!湖北双面板PCB电路板加工生产商

电路板上的贴片元件怎么焊接与拆?上海PCB贴片PCB电路板元器件

有一些工程师在创建PCB时,往往会在板上留下许多无铜区域。但PCB板上高比例的无铜区域会对产品产生负面影响,使其容易受到早期损坏,这个时候铜浇注就派上用场了。有一些新手认为更少的铜浇筑意味着成本也会越来越低,那就错了。确实电镀面积小,可以节省铜,但是质量的话就没有办法保证,适量的铜浇注可以提高产品的质量。当 PCB 板放入电镀槽中,施加适当的电流可时,PCB就会呈现出现干膜覆盖后的物理状态。露在干膜之外的部分电路的总面积会影响电镀过程中电流分布的值,如果是裸铜面积大,电流输入均匀,接收到的电流更均匀。因此设计时必须大面积铺铜平面,防止这种情况发生。如果铜的总电镀面积太小或者图案分布很不均匀,接收的电流也不会均匀。这样,通电时,电流越大,镀铜层越厚(这样设计的话,如果只要求1OZ,那么成品铜厚就可以达到2OZ)。如果电流迹线之间的间隙太小,例如大约 3mil 到 3.5mil,则会在迹线之间形成“夹膜”。换句话说,干膜夹在间隙的中间,会导致随后的基极开始的铜位于中间,如果蚀刻过程没有清洗干净,可能会导致短路上海PCB贴片PCB电路板元器件