商机详情 -

绵阳陶瓷晶振

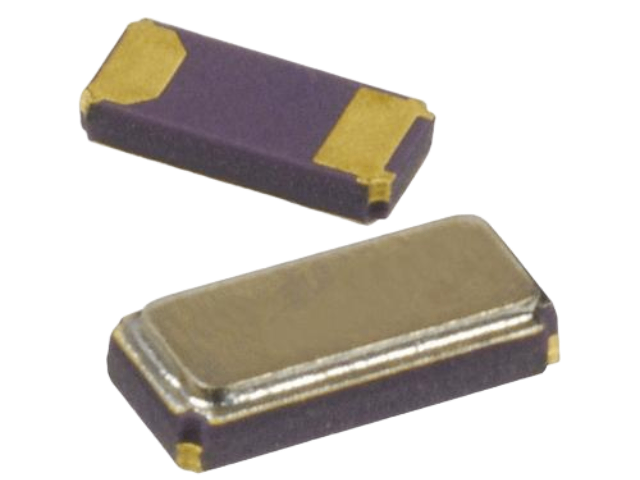

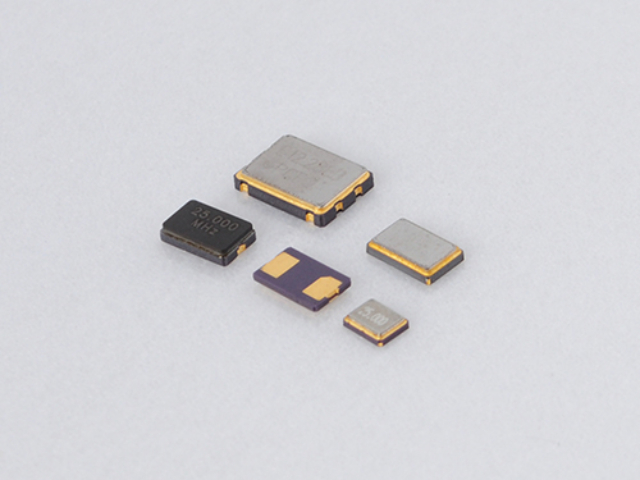

先进陶瓷晶振通过材料革新与工艺突破,已实现小型化、高频化、低功耗化的跨越式发展,成为电子设备升级的关键推手。在小型化领域,采用超薄陶瓷基板(厚度低至 50μm)与立体堆叠封装技术,使晶振尺寸从传统的 5×3.2mm 缩减至 0.8×0.6mm,只为指甲盖的 1/20,却能保持完整的谐振结构 —— 这种微型化设计完美适配智能手表、医疗贴片等穿戴设备,在有限空间内提供稳定频率输出。高频化突破则依托掺杂改性的锆钛酸铅陶瓷,其压电系数提升 40%,谐振频率上限从 6GHz 跃升至 12GHz,可满足 6G 通信原型机的毫米波载波需求。在高频模式下,频率稳定度仍维持在 ±0.05ppm,确保高速数据传输中每比特信号的时序精度,使单通道数据速率突破 100Gbps。工业控制少不了陶瓷晶振,它为设备提供稳定时钟与计数器信号。绵阳陶瓷晶振

在科技飞速发展的浪潮中,陶瓷晶振凭借持续突破的性能上限,成为电子元件领域备受瞩目的 “潜力股”。材料革新是其性能跃升的驱动力,新型掺杂陶瓷(如铌酸钾钠基无铅陶瓷)的应用,使频率稳定度较传统材料提升 40%,在 - 60℃至 180℃的极端温差下,频率漂移仍能控制在 ±0.3ppm 以内,为航空航天等领域提供了更可靠的频率基准。技术迭代不断解锁其性能边界,通过纳米级薄膜制备工艺,陶瓷晶振的振动能量损耗降低至 0.1dB/cm 以下,工作效率突破 92%,在相同功耗下可输出更强的频率信号。同时,多频集成技术实现单颗晶振支持 1MHz-200MHz 全频段可调,满足复杂电子系统的多场景需求,替代传统多颗分立元件,使电路集成度提升 50% 以上。青岛陶瓷晶振批发作为时钟源、频率发生器等多功能元件,陶瓷晶振用途广。

陶瓷晶振采用内置负载电容的集成设计,使振荡电路无需额外配置外部负载电容器,这种贴心设计为电子工程师带来了便利。传统晶振需根据振荡电路的阻抗特性,外接 2-3 个精密电容(通常为 6pF-30pF)来匹配谐振条件,而陶瓷晶振通过在内部基座与上盖之间集成薄膜电容层,预设 12pF、18pF、22pF 等常用负载值,可直接与 555 定时器、MCU 振荡引脚等电路无缝对接,省去了复杂的电容参数计算与选型步骤。从实际应用来看,这种设计能减少 PCB 板上 30% 的元件占位面积 —— 以 1.6×1.2mm 的陶瓷晶振为例,其内置电容无需额外 0.4×0.2mm 的贴片电容空间,使智能手环、蓝牙耳机等微型设备的电路布局更从容。在生产环节,少装 2 个外部电容可使 SMT 贴装效率提升 15%,同时降低因电容虚焊、错装导致的故障率(实验数据显示,相关不良率从 2.3% 降至 0.5%)。

采用黑色陶瓷面上盖的陶瓷晶振,在避光与电磁隔离性能上实现了突破,为精密电子系统提供了更可靠的频率保障。黑色陶瓷盖体采用特殊的氧化锆基材料,通过添加钒、铬等过渡金属氧化物形成致密的遮光结构,对可见光与近红外光的吸收率达 95% 以上,能有效阻断外界光线对内部谐振腔的干扰 —— 实验数据显示,在强光照射环境下,其频率漂移量较普通透明盖体晶振降低 80%,确保光学仪器、户外监测设备等场景中的频率稳定性。在电磁隔离方面,黑色陶瓷经高温烧结形成的多晶结构具有 10^12Ω・cm 以上的体积电阻率,配合表面纳米银层的接地设计,可构建高效电磁屏蔽屏障,对 100kHz-1GHz 频段的电磁干扰衰减量超过 40dB。这意味着在手机主板、工业控制柜等电磁环境复杂的场景中,晶振输出信号的信噪比提升至 60dB 以上,避免了电磁耦合导致的频率抖动。作为微处理器时钟振荡器匹配元件,陶瓷晶振应用范围很广。

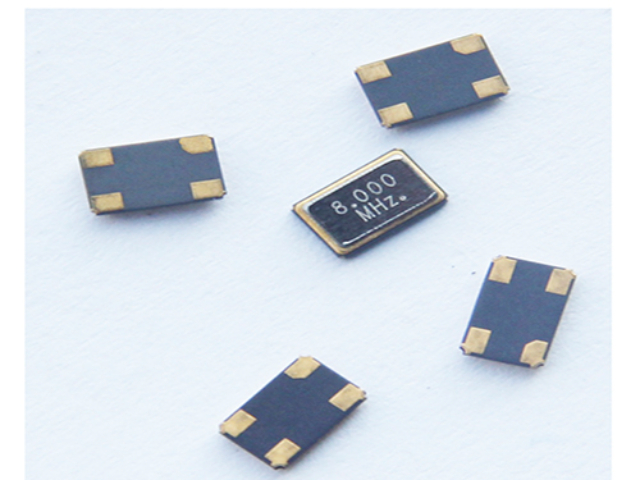

陶瓷晶振凭借精巧设计实现高密度安装,同时通过全链条成本优化展现超高性价比。在高密度安装方面,其采用超小型化封装,较传统石英晶振节省 60% 以上 PCB 空间,配合标准化 SMT 表面贴装设计,引脚间距缩小至 0.2mm,可在 1cm² 面积内实现 30 颗以上的密集排布,完美适配智能手机主板、可穿戴设备等高密度电路场景。这种紧凑设计兼容自动化贴装设备,贴装效率提升至每小时 3 万颗,大幅降低人工干预成本。成本控制贯穿全生命周期:材料上采用 93 氧化铝陶瓷等量产型基材,较特种晶体材料采购成本降低 40%;生产端通过一体化烧结工艺实现 99.5% 的良率,规模化生产使单位制造成本下降 30%;应用端因内置负载电容等集成设计,减少 2-3 个元件,物料清单(BOM)成本降低 15%-20%。陶瓷晶振内藏不同电容值,可对应不同 IC,灵活又实用。江西YXC陶瓷晶振应用

陶瓷晶振,电子设备的 “心跳器”,以稳定频率驱动各类电路高效运转。绵阳陶瓷晶振

陶瓷晶振作为计算机 CPU、内存等部件的基准时钟源,以频率输出支撑着高速运算的有序进行。在 CPU 中,其提供的高频时钟信号(可达 5GHz 以上)是指令执行的 “节拍器”,频率精度控制在 ±0.1ppm 以内,确保每一个运算周期的时间误差不超过 0.1 纳秒,使多核处理器的 billions 次指令能协同同步,避免因时序错乱导致的运算错误。内存模块的读写操作同样依赖陶瓷晶振的稳定驱动。在 DDR5 内存中,其 1.6GHz 的时钟频率可实现每秒 80GB 的数据传输速率,而陶瓷晶振的频率抖动控制在 5ps 以下,能匹配内存控制器的寻址周期,确保数据读写的时序对齐,将内存访问延迟压缩至 10 纳秒级,为 CPU 高速缓存提供高效数据补给。绵阳陶瓷晶振