商机详情 -

重庆国产管式炉PSG/BPSG工艺

氧化工艺中管式炉的不可替代性:热氧化是半导体器件制造的基础步骤,管式炉在干氧/湿氧氧化中表现优异。干氧氧化(如1000°C下生成SiO₂)生长速率慢但薄膜致密,适用于栅氧层;湿氧氧化(通入H₂O蒸气)速率快但多孔,常用于场氧隔离。管式炉的多段控温可精确调节氧化层的厚度(±0.1 nm),而传统批次式设计(50–100片/次)仍具成本优势。近年来,部分产线采用快速氧化管式炉(RTO)以缩短周期,但高温稳定性仍依赖传统炉体结构。管式炉制备半导体量子点效果优良。重庆国产管式炉PSG/BPSG工艺

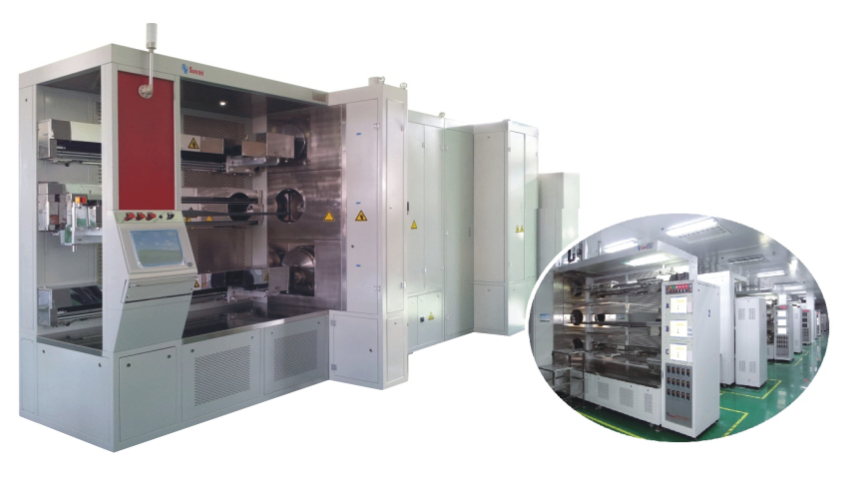

管式炉在金属硅化物(如TiSi₂、CoSi₂)形成中通过退火工艺促进金属与硅的固相反应,典型温度400℃-800℃,时间30-60分钟,气氛为氮气或氩气。以钴硅化物为例,先在硅表面溅射50-100nm钴膜,随后在管式炉中进行两步退火:第一步低温(400℃)形成Co₂Si,第二步高温(700℃)转化为低阻CoSi₂,电阻率可降至15-20μΩ・cm。界面质量对硅化物性能至关重要。通过精确控制退火温度和时间,可抑制有害副反应(如CoSi₂向CoSi转化),并通过预氧化硅表面(生长2-5nmSiO₂)阻止金属穿透。此外,采用快速热退火(RTA)替代常规管式退火,可将退火时间缩短至10秒,明显减少硅衬底中的自间隙原子扩散,降低漏电流风险。苏州赛瑞达管式炉POCL3扩散炉管式炉支持多工位设计,提升生产效率,适合批量生产,点击查看!

精确控温对于半导体管式炉的性能至关重要。以某品牌管式炉为例,其搭载智能 PID 温控系统,温度波动低可小于 0.5 摄氏度,在氧化工艺中,能将氧化膜厚度误差控制在小于 2%,确保每一片晶圆都能获得高度一致且精确的热处理,满足半导体制造对工艺精度的极高要求,提升了产品的稳定性与可靠性。随着半导体产业的快速发展,管式炉市场规模持续增长。据相关报告预测,2025 年全球管式炉市场规模预计达 60 亿元,到 2030 年将突破 80 亿元,年复合增长率约 6% - 8%。这一增长主要由半导体等产业的强劲需求拉动,尤其是中国半导体产业快速发展,预计 2025 年新增多条 12 英寸晶圆生产线,对高级管式炉的需求将进一步激增。

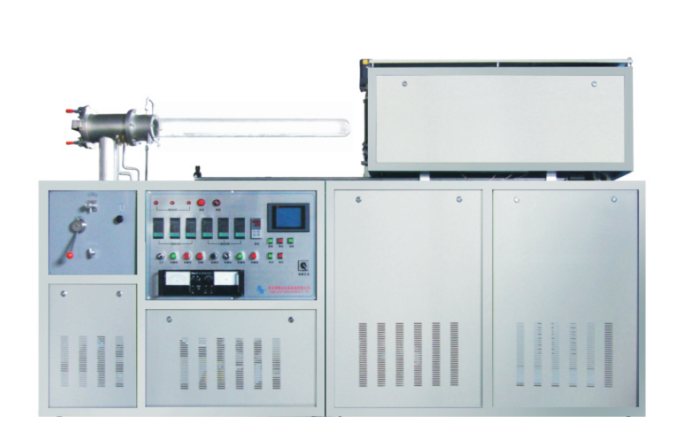

在半导体制造进程中,薄膜沉积是一项极为重要的工艺,而管式炉在其中发挥着关键的精确操控作用。通过化学气相沉积(CVD)等技术,管式炉能够在半导体硅片表面精确地沉积多种具有特定功能的薄膜材料。以氮化硅(SiN)薄膜和二氧化硅(SiO2)薄膜为例,这两种薄膜在半导体器件中具有广泛应用,如作为绝缘层,能够有效隔离不同的导电区域,防止漏电现象的发生;还可充当钝化层,保护半导体器件免受外界环境的侵蚀,提高器件的稳定性和可靠性。在进行薄膜沉积时,管式炉能够提供精确且稳定的温度环境,同时对反应气体的流量、压力等参数进行精确控制。管式炉用于金属退火、淬火、粉末烧结等热处理工艺,提升材料强度与耐腐蚀性。

随着半导体技术的持续发展,新型半导体材料,如二维材料(石墨烯、二硫化钼等)、有机半导体材料等的研发成为了当前的研究热点,管式炉在这些新型材料的研究进程中发挥着重要的探索性作用。以二维材料的制备为例,管式炉可用于化学气相沉积法生长二维材料薄膜。在管式炉内,通过精确控制温度、反应气体的种类和流量等条件,能够实现对二维材料生长过程的精细调控。例如,在生长石墨烯薄膜时,将含有碳源的气体通入管式炉内,在高温环境下,碳源分解并在衬底表面沉积,形成石墨烯薄膜。赛瑞达管式炉优化气流,实现半导体 CVD 薄膜高品沉积,等您来电!东北第三代半导体管式炉掺杂POLY工艺

管式炉适用于晶园退火、氧化等工艺,提升半导体质量,欢迎咨询!重庆国产管式炉PSG/BPSG工艺

在半导体CVD工艺中,管式炉通过热分解或化学反应在衬底表面沉积薄膜。例如,生长二氧化硅(SiO₂)绝缘层时,炉内通入硅烷(SiH₄)和氧气,在900°C下反应生成均匀薄膜。管式炉的线性温度梯度设计可优化气体流动,减少湍流导致的膜厚不均。此外,通过调节气体流量比(如TEOS/O₂),可控制薄膜的介电常数和应力。行业趋势显示,低压CVD(LPCVD)管式炉正逐步兼容更大尺寸晶圆(8英寸至12英寸),并集成原位监测模块(如激光干涉仪)以提升良率。