商机详情 -

车规级差分输出VCXO按需定制

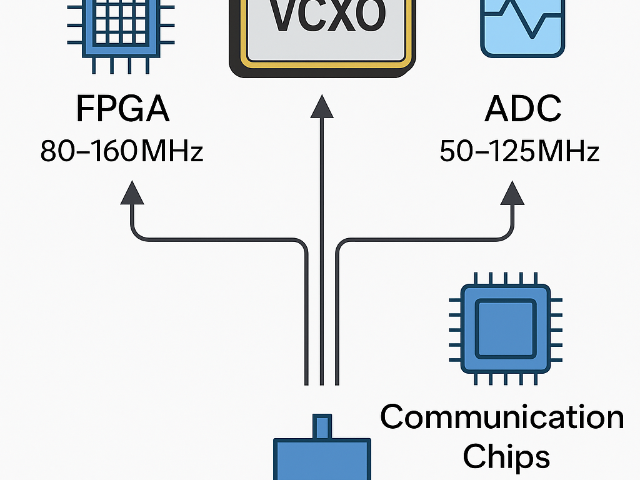

差分输出VCXO优化FPGA SerDes链路时钟 FPGA内置的SerDes模块是实现高速串行通信的关键接口,差分时钟源是其性能表现的关键。FCom富士晶振差分输出VCXO通过精确频率控制与低相位抖动,为FPGA链路提供稳定的参考时钟。 在Xilinx Kintex、Intel Stratix等系列FPGA中,TX/RX PLL对时钟源的抖动容忍度有限。FCom VCXO输出的LVPECL或LVDS信号具备高信号完整性,帮助PLL稳定锁相,减少链路抖动传递。 该系列支持可编程频率调节(如125MHz、156.25MHz、200MHz),满足以太网、PCIe、Aurora等协议栈的定频需求。频率拉动值支持±50~150ppm调谐,便于与系统主控同步校准。 FCom富士晶振VCXO采用金属密封封装,具有良好抗热漂性能,在高温工况下依然保持±25ppm稳定性,适配FPGA开发板、通信主控卡及背板互连设备。 通过将FCom的差分输出VCXO部署于SerDes路径,可有效抑制串扰与时钟歪斜,提高数据眼图开口率与误码性能,为高速接口提供可靠时钟支撑。差分输出VCXO可提升SerDes时钟链的精度。车规级差分输出VCXO按需定制

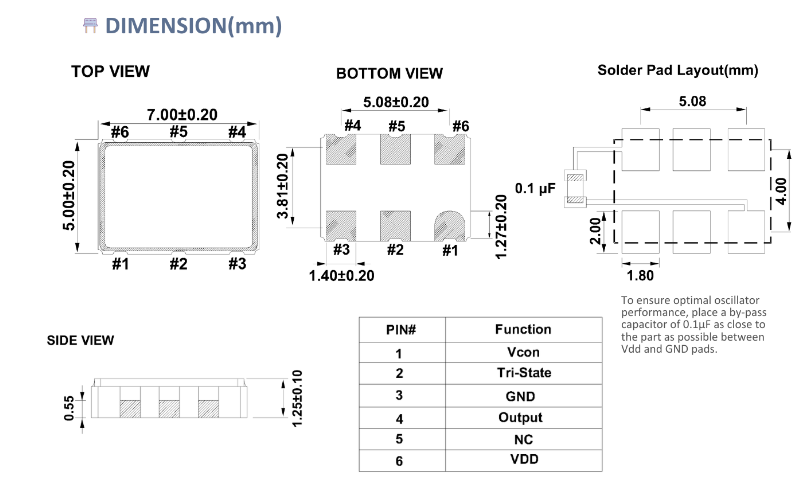

差分VCXO优化嵌入式系统的总线定时 嵌入式系统如工业控制板、智能传感器、边缘计算模组等需要在尺寸有限条件下,实现高精度、低功耗的总线通信时序控制。差分VCXO正是满足该类场景的高集成时钟方案。 FCom富士晶振VCXO具备20MHz~100MHz频率可选,适配STM32H7、TI Sitara、Raspberry Pi CM模块等常用SoC平台。 LVDS输出接口提供高速、低电磁干扰特性,适配SPI、I2S、UART等多种嵌入式协议总线的高速传输需求。 ±50ppm可调拉频功能支持系统启动后进行频率自校准,有效提升I2C时钟精度、ADC采样率一致性与多模块间协调性。 封装采用3225、2520小型化设计,适配高集成主板或模块化布局,满足超小尺寸与低功耗需求场合。 FCom差分VCXO为嵌入式系统提供可靠、灵活的频率基准,是支持其稳定运行与多模块协同通信的时钟中枢。可靠性高差分输出VCXO厂家电话差分输出VCXO有助于控制系统级的时钟漂移。

差分VCXO为AI边缘系统提供稳定定时源 边缘AI系统需要进行本地数据分析与模型推理,其内部搭载的神经网络加速器、AI SoC及GPU协同模块依赖统一时钟源进行高速协作。差分VCXO正是这些多模块平台理想的同步方案。 FCom富士晶振支持100MHz、125MHz、156.25MHz频率,适配如NVIDIA Jetson Orin、Hailo-8、Kneron KL730等边缘推理芯片的时钟输入接口。 低抖动(<0.2ps)特性减少高速DDR数据与USB3.0、PCIe之间传输延迟差异,避免AI推理模块在时间轴上出现偏差。 ±100ppm拉频能力允许主控AI调度器在功耗变化或输入信号变化下实时微调时钟,保证感知层与决策层协同作业。 高可靠7050封装适用于工业AI网关、边缘智能摄像机、AI机器人等需要24/7运行的场景,维持系统高可用性。 FCom差分VCXO为边缘AI应用构建了坚固的时间骨架,是实现智能判断准确性的定时关键。

差分VCXO支持工业级NVMe存储平台定时 工业服务器与嵌入式存储平台的高速NVMe接口对参考时钟抖动与精度要求极高。差分VCXO为数据一致性与低延迟读写提供时钟基础。 FCom富士晶振差分VCXO支持100MHz、125MHz、200MHz频率,适配于Intel P4510、Kioxia CD7、Micron 7400等NVMe控制平台。 抖动小于0.2ps,确保PCIe Gen4/5通道中链路训练与EQ过程中的信号稳定,避免频率偏移带来的传输中断。 可调拉频设计支持系统启动后进行时钟同步微调,配合时钟缓冲器与分配器,形成多通道定时参考源。 产品提供多种封装规格,适用于U.2、M.2、E1.S、E3.S等高密度模块,具备良好电源噪声隔离特性。 FCom差分VCXO是工业级存储设备中维系数据稳定与接口高速运行不可或缺的定时关键器件。差分输出VCXO具有良好的频率调节特性。

差分VCXO优化边缘服务器的时钟架构 边缘服务器在处理本地AI运算、IoT网关控制、实时图像识别等任务时,面临数据传输、存储与计算多路径调度问题,需好品质时钟支撑系统协调运行。 FCom差分VCXO支持包括100MHz、125MHz、200MHz等边缘计算常用频率,适配Intel Xeon D、NXP Layerscape、Ampere Altra等芯片平台。 低至0.15ps的相位抖动帮助系统实现NVMe数据同步、PCIe控制器稳定通信、DDR内存读取准确性等多个模块的信号配合。 VCXO支持可编程电压控制,可灵活适配平台中负载变化带来的时钟差异,通过I2C/DAC控制完成自动调谐。 封装采用7050高热散设计,带有防护金属罩,适用于设备密集部署与高热流区域,确保时钟质量长时间维持在稳定范围。 FCom差分VCXO帮助边缘计算设备构建精密的定时平台,是保证边缘AI与分布式节点系统高效协同的重要基石。差分输出VCXO是数字通信系统的时钟基准源。多输出差分输出VCXO商家

差分输出VCXO优化了FPGA中的参考时钟链。车规级差分输出VCXO按需定制

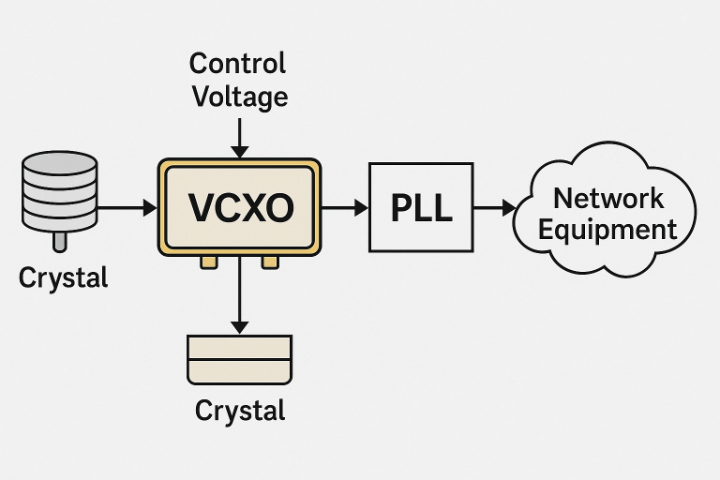

差分VCXO在多协议同步平台中的整合优势 现代通信设备需同时支持多种协议,如以太网、PCIe、SATA、USB等,每个协议对参考时钟的稳定性和精度要求不同。差分VCXO成为多协议融合设备的理想时钟方案。 FCom富士晶振差分输出VCXO支持10MHz~250MHz频率覆盖,可为多通道PHY、MAC控制器、同步网络提供统一时钟基准,尤其适配Broadcom、TI、NXP等常用SoC平台。 通过LVDS/HCSL输出接口,系统可实现高精度多频切换,单晶体系统中频率不足或兼容性差的问题,实现软硬件兼容性大化。 可编程拉频功能(±100ppm)可与I2C/DAC控制系统配合,实现协议之间时钟交错、握手校正与同步误差抵消,是跨协议通信平台关键功能模块之一。 封装具备高可靠性与高屏蔽能力,适用于工业级、通信级与嵌入式平台,有效抑制串扰与EMI问题,提升通信信道完整性。 FCom差分VCXO通过高性能的频率支持与灵活调控机制,为多协议同步平台提供统一、精确的时钟支撑,是高集成系统不可或缺的关键器件。车规级差分输出VCXO按需定制