商机详情 -

FVC7LPG差分输出VCXO欢迎选购

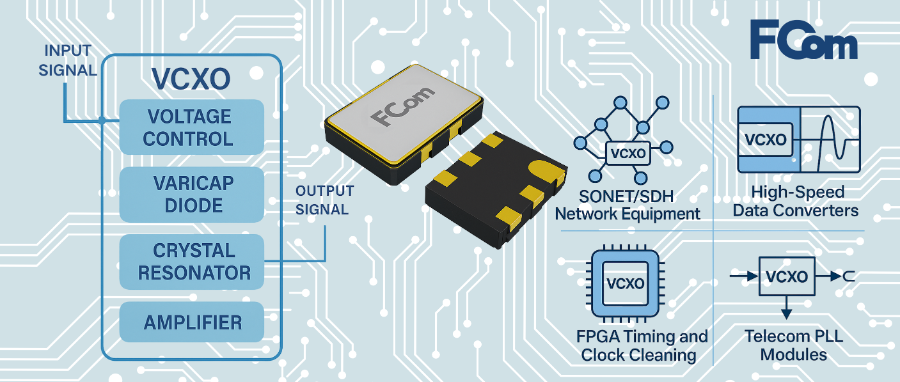

差分VCXO在轨道交通控制系统的关键作用 轨道交通中的列车自动控制系统(CBTC)、信号通信系统与车载网络均需依赖统一的高可靠时钟源。差分VCXO是实现地面与车载系统精确通信的定时关键。 FCom差分VCXO提供50MHz、100MHz标准频点,适配于车地通信单元、数据记录仪、控制器通信模块等关键装置。 产品支持LVDS与HCSL输出格式,可与MVB、ETHERNET、CAN等轨交控制总线完美对接,降低传输误码率。 VCXO具备抗震、防磁、高温容忍能力,在车辆运行震动、强磁干扰、高温长时工作等环境下稳定输出。 ±100ppm拉频功能用于不同运行段控制策略之间的时钟微调,实现列车分级管控与故障诊断的时序保障。 FCom差分VCXO已广部署于地铁、高铁、城际列车等系统,是现代轨道交通安全运行的时钟中坚力量。差分输出VCXO可提升SerDes时钟链的精度。FVC7LPG差分输出VCXO欢迎选购

差分VCXO在PCIe平台中的参考时钟应用 PCIe作为主流高速互联总线,其主控芯片、桥接器与终端设备需采用统一参考时钟以实现链路建立与稳定通信。FCom富士晶振差分输出VCXO为此类系统提供高质量差分时钟输出。 在x4、x8、x16通道架构下,100MHz HCSL时钟是常见选择,FCom VCXO具备低于0.2ps抖动的HCSL输出版本,适配主板、网络卡、RAID控制器等系统设计。 其±100ppm可调特性允许在系统初始化阶段配合PHY进行链路同步微调,确保训练过程稳定完成。 FCom产品支持2520/3225等紧凑型封装,便于在多层PCB中布线,降低耦合噪声与互联干扰。 其差分输出信号上升沿对称性好,匹配PCIe 4.0/5.0标准对Jitter Budget的要求,满足高速系统严苛信号质量标准。 选用FCom差分输出VCXO可突出提升PCIe总线稳定性、降低误码率,是构建高速互联平台的重要时钟模块。抗干扰差分输出VCXO商家差分输出VCXO为毫米波通信模块提供精确时钟。

差分VCXO在高速ADC模块中的抖动控制 高速模数转换器(ADC)广应用于雷达、通信、医疗成像等领域,其精度高度依赖于参考时钟的稳定性和抖动控制。VCXO作为参考源,尤其是具备差分输出的低抖动版本,可极大提升采样系统的信噪比与分辨率。 FCom富士晶振的差分VCXO产品支持125MHz、250MHz、500MHz等常用ADC参考频率,具备<0.15ps的低抖动特性,适配TI ADS54J系列、Analog AD9208系列等前沿采样芯片。 差分LVDS或LVPECL接口可直接驱动ADC的采样时钟输入端,并通过高对称性和边沿精确性降低采样延迟误差,提升系统的动态性能与采样精度。 在需要动态采样率调整的系统中,FCom VCXO的±100ppm拉频能力可以实现灵活调谐,适应不同带宽、信号源或同步策略的应用环境。 产品采用金属上盖陶瓷封装,提供良好的EMI屏蔽效果和热稳定性,使其在多通道、高密度ADC模块中稳定运行,避免时钟污染与串扰。 FCom差分VCXO为ADC采样提供精确低噪声时钟支撑,是提升信号处理系统性能的关键组件,尤其适用于高频、高速和高精度测量场景。

差分VCXO为AI边缘系统提供稳定定时源 边缘AI系统需要进行本地数据分析与模型推理,其内部搭载的神经网络加速器、AI SoC及GPU协同模块依赖统一时钟源进行高速协作。差分VCXO正是这些多模块平台理想的同步方案。 FCom富士晶振支持100MHz、125MHz、156.25MHz频率,适配如NVIDIA Jetson Orin、Hailo-8、Kneron KL730等边缘推理芯片的时钟输入接口。 低抖动(<0.2ps)特性减少高速DDR数据与USB3.0、PCIe之间传输延迟差异,避免AI推理模块在时间轴上出现偏差。 ±100ppm拉频能力允许主控AI调度器在功耗变化或输入信号变化下实时微调时钟,保证感知层与决策层协同作业。 高可靠7050封装适用于工业AI网关、边缘智能摄像机、AI机器人等需要24/7运行的场景,维持系统高可用性。 FCom差分VCXO为边缘AI应用构建了坚固的时间骨架,是实现智能判断准确性的定时关键。差分输出VCXO在电信与广播领域被高度信赖。

差分输出VCXO在高速ADC系统中的应用价值 在高速数据采集系统中,ADC(模数转换器)的采样精度直接依赖于参考时钟的抖动性能。FCom富士晶振推出的差分输出VCXO,凭借低抖动设计,成为高性能ADC系统的关键时钟来源。 高速ADC(如TI ADS54J60、Analog Devices AD9680)广支持差分时钟输入接口,要求RMS抖动低于1ps。FCom差分VCXO在典型配置下可实现0.6ps~0.15ps级别的低抖动输出,为采样保持环节提供高信噪比保障。 该系列产品支持HCSL/LVDS差分标准,可灵活集成至多通道数据采集板卡,适配PCIe采集卡、测试仪器、雷达信号处理等应用。用户可通过电压控制引脚(VCTRL)进行中心频率微调,匹配PLL或同步采样结构。 FCom富士晶振的差分VCXO具备±25ppm稳定性与长时间可靠性,封装形态包括3225与5032,便于PCB差分走线与时钟引出布线设计,缩短工程验证周期。 通过部署FCom差分输出VCXO,高速ADC采集系统可获得更低采样噪声、更宽带宽支持及更高系统灵敏度,为工业测试与通信信号分析提供坚实时钟支持。差分输出VCXO支持小尺寸封装,适配微型模块。新型差分输出VCXO电话

差分输出VCXO支持跨平台的接口兼容设计。FVC7LPG差分输出VCXO欢迎选购

差分VCXO优化嵌入式系统的总线定时 嵌入式系统如工业控制板、智能传感器、边缘计算模组等需要在尺寸有限条件下,实现高精度、低功耗的总线通信时序控制。差分VCXO正是满足该类场景的高集成时钟方案。 FCom富士晶振VCXO具备20MHz~100MHz频率可选,适配STM32H7、TI Sitara、Raspberry Pi CM模块等常用SoC平台。 LVDS输出接口提供高速、低电磁干扰特性,适配SPI、I2S、UART等多种嵌入式协议总线的高速传输需求。 ±50ppm可调拉频功能支持系统启动后进行频率自校准,有效提升I2C时钟精度、ADC采样率一致性与多模块间协调性。 封装采用3225、2520小型化设计,适配高集成主板或模块化布局,满足超小尺寸与低功耗需求场合。 FCom差分VCXO为嵌入式系统提供可靠、灵活的频率基准,是支持其稳定运行与多模块协同通信的时钟中枢。FVC7LPG差分输出VCXO欢迎选购