商机详情 -

超宽温可编程差分振荡器生产企业

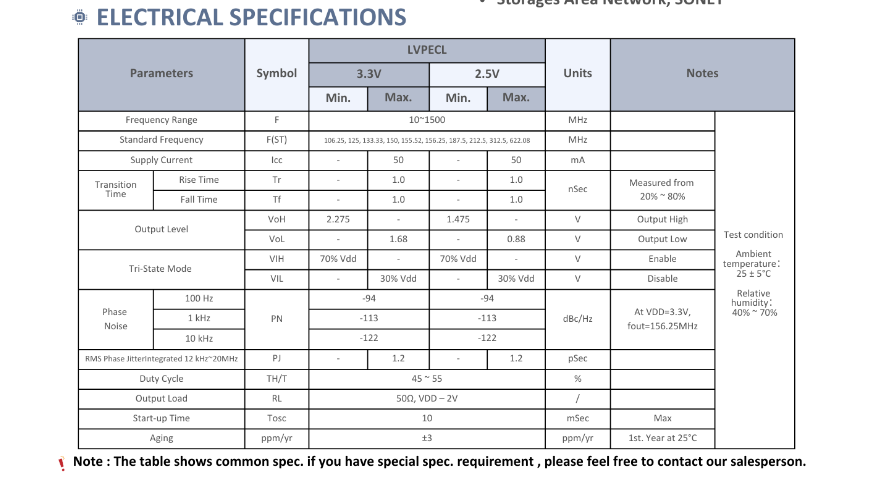

相比传统频率定制需要晶体重新裁片、长周期流片,FCom可编程差分振荡器可快速交付样品,需电编或出厂设定即可实现定制频率,大幅提升研发效率与BOM灵活性。同时,产品支持多种电压平台(1.8V/2.5V/3.3V),支持-40~125°C工业与车规宽温版本,封装尺寸覆盖2520/3225等四种常规规格。 FCom差分振荡器内置高精度PLL与低相位噪声VCXO架构,结合数字温度补偿算法,在宽温环境中依然维持稳定输出,适配复杂工业、通信与AI计算场景。其Enable控制与OE功能支持系统级动态启用/屏蔽功能,便于多时钟域管理。通过FCom专属配置工具,可实现快速频率配置、接口仿真和系统级兼容性校准,降低客户集成复杂度。无线传输链路中可编程差分振荡器提供精确载波。超宽温可编程差分振荡器生产企业

可编程差分振荡器

边缘渲染终端的多通道图像处理时钟支持 边缘渲染终端各个方面部署于AR/VR边缘处理、沉浸式显示、广告一体机与本地转码节点等场景,需同时处理多通道高清视频流与AI识别任务。其系统结构通常包含多个图像采集通道、GPU/FPGA渲染关键、多输出控制器与边缘智能处理模组。FCom富士晶振可编程差分振荡器为此类设备构建稳定、灵活、高质量的统一时钟平台。 支持视频标准频点27MHz、74.25MHz、148.5MHz及接口频点100MHz、125MHz、156.25MHz输出,可在一颗芯片内提供多个频点,简化分频结构设计。接口支持HCSL/LVDS/PECL,灵活适配GPU模块、视频输入芯片与显示控制IC。 系统内不同模块间需高度同步,FCom产品支持多路输出控制、OE分通道屏蔽与动态启动配置,提升渲染帧同步效率与响应速度。 其抗EMI干扰设计可降低视频干扰纹波,提高屏幕一致性。产品已被部署于广告播控设备、AR边缘渲染引擎、沉浸会议辅助终端中,成为多通道渲染系统的标准时钟配置。高性能可编程差分振荡器诚信合作卫星通信终端中各个方面采用可编程差分振荡器输出基频。

大规模FPGA设计项目中的统一时钟架构构建 在通信基站、图像处理平台、测试测量设备、AI网关等多个场景中,FPGA作为关键处理单元需同时管理多个时钟域(输入同步、IO驱动、PLL控制、AXI总线),设计中存在频率出错、资源浪费与同步偏移风险。FCom富士晶振可编程差分振荡器提供统一频率源与灵活配置方式,为大规模FPGA设计提供集中管理的可控时钟结构。 FCom产品支持多频输出(如24MHz、50MHz、100MHz、125MHz、156.25MHz、200MHz),具备LVDS/HCSL多接口配置能力,可连接至FPGA外部时钟输入口、IO Bank参考时钟、PLL Clock-IN与内部逻辑触发器。输出抖动低至0.1ps,保障时序余量。 通过FCom提供的GUI工具,用户可快速配置目标频率组合并仿真接口兼容性,提升工程调试效率。产品支持1.8V~3.3V工作平台,适应不同FPGA品牌(Xilinx、Intel、Lattice、Microchip等)IO电压标准。

可编程振荡器在5G前传设备中的灵活部署 5G通信网络由CU(集中单元)、DU(分布单元)和RU(远端射频单元)三部分构成,其中DU和RU之间通过eCPRI进行高速前传通信,对时钟同步精度和灵活部署能力提出极高要求。FCom富士晶振的可编程差分振荡器,在满足eCPRI、SyncE、1588v2等时钟协议的基础上,提供灵活、精确的频率配置能力,各个方面应用于5G前传设备中。 例如,DU中需要提供基准频率156.25MHz以支撑25G SFP28光模块;在RU模块中则需提供122.88MHz频点以驱动AD9361/AD9371射频芯片。FCom振荡器可通过配置器件实现不同频点动态切换,也可预设双频点工作状态,通过GPIO或I²C接口实现切换逻辑。 产品具备抗电磁干扰(EMI)设计、低相位噪声特性、封装紧凑等优势,可直接部署在紧凑型基站、微基站、室内覆盖设备、小区RRU等场景,支持PoE供电或远程配置系统部署。其可编程特性极大提升了产品SKU复用率,有效降低运营商项目集采中的BOM复杂度。嵌入式图像系统选用可编程差分振荡器提升图像一致性。

可编程特性使得用户可根据视频标准(如HD-SDI、3G-SDI、12G-SDI)快速配置目标频率,适配多种分辨率与帧率格式。 此外,FCom产品支持双频输出配置,可作为主帧同步时钟与采集端编码同步源,实现双端一致性。其封装支持3225/5032等,适合部署于视频编辑控制台、直播推流服务器、视频矩阵、内容传输节点中。 目前FCom差分振荡器已被多家专业广播设备厂商采纳,用于大型演播室系统、8K直播编解码平台、高帧率电影制作链路,为专业图像质量提供时钟基准支撑。差分输出结构提升了可编程差分振荡器的抗干扰能力。可编程差分振荡器供应商

通过I2C或SPI控制可编程差分振荡器参数更改。超宽温可编程差分振荡器生产企业

高速SerDes链路中的Jitter抑制解决方案 SerDes(串并转换器)作为现代高速通信链路的关键模块,其性能直接受参考时钟信号抖动与相位稳定性的影响。尤其在PCIe Gen4/Gen5、10G/25G/56G Ethernet、USB4、SATA等高速链路中,SerDes对参考时钟的RMS抖动容差通常在0.15ps以下。FCom富士晶振推出的可编程差分振荡器,正是为满足高速SerDes链路严苛抖动规范而设计。 该系列产品采用低噪声PLL与高线性VCXO内核设计,有效抑制输出Jitter,实际测试中可提供低至0.05ps RMS的优异表现,支持多种差分输出标准(LVDS、LVPECL、HCSL),同时具备±25ppm/±50ppm频稳可选,适配不同信号敏感度需求。超宽温可编程差分振荡器生产企业