商机详情 -

北京模组封装测试

对于堆叠结构,可以区分如下几种:芯片堆叠、PoP、PiP、TSV。堆叠芯片,是一种两个或更多芯片堆叠并粘合在一个封装中的组装技术。这较初是作为一种将两个内存芯片放在一个封装中以使内存密度翻倍的方法而开发的。 无论第二个芯片是在头一个芯片的顶部还是在它旁边,都经常使用术语“堆叠芯片”。技术已经进步,可以堆叠许多芯片,但总数量受到封装厚度的限制。芯片堆叠技术已被证明可以多达 24 个芯片堆叠。然而,大多数使用9 芯片高度的堆叠芯片封装技术的来解决复杂的测试、良率和运输挑战。芯片堆叠也普遍应用在传统的基于引线框架的封装中,包括QFP、MLF 和 SOP 封装形式。如下图2.21的堆叠芯片封装形式。SiP系统级封装以其更小、薄、轻和更多功能的竞争力,为芯片和器件整合提供了新的可能性。北京模组封装测试

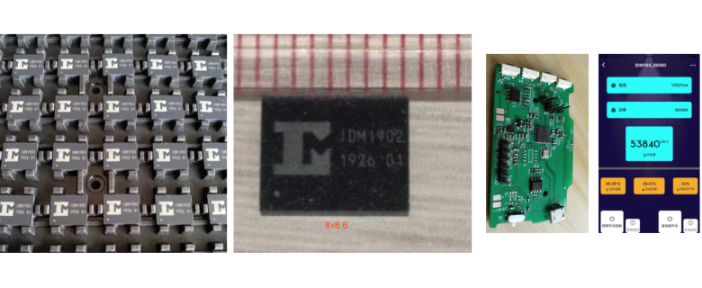

SiP系统级封装(SiP)制程关键技术,高密度打件,在高密度打件制程方面,云茂电子已达到约为婴儿发丝直径的40μm。以10x10被动组件数组做比较,大幅缩减超过70%的主板面积,其中的40%乃源自于打件技术的突破。 塑封 由于高密度打件采用微小化元器件与制程,因此元器件与载板之间的连结,吃锡量大幅减少,为提高打件可靠度,避免外界湿度、高温及压力等影响,塑封制程可将完整的元器件密封包覆在载板上。相较于一般委外封测(OSAT)塑封约100颗左右,云茂电子的系统级封装塑封技术,则是可容纳高达900颗组件。 北京模组封装测试SiP是理想的解决方案,综合了现有的芯核资源和半导体生产工艺的优势,降低成本,缩短上市时间。

SiP 封装优势:1)封装面积增大,SiP在同一个封装种叠加两个或者多个芯片。把垂直方向的空间利用起来,同时不必增加引出管脚,芯片叠装在同一个壳体内,整体封装面积较大程度上减少。2)采用超薄的芯片堆叠与TSV技术使得多层芯片的堆叠封装体积减小,先进的封装技术可以实现多层芯片堆叠厚度。3)所有元件在一个封装壳体内,缩短了电路连接,见笑了阻抗、射频、热等损耗影响。提高了光,电等信号的性能。4)SiP 可将不同的材料,兼容不同的GaAs,Si,InP,SiC,陶瓷,PCB等多种材料进行组合进行一体化封装。

SiP具有以下优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。汽车汽车电子是 SiP 的重要应用场景。

SiP系统级封装需求主要包括以下几个方面:1、精度:先进封装对于精度的要求非常高,因为封装中的芯片和其他器件的尺寸越来越小,而封装密度却越来越大。因此,固晶设备需要具备高精度的定位和控制能力,以确保每个芯片都能准确地放置在预定的位置上。2、速度:先进封装的生产效率对于封装成本和产品竞争力有着重要影响。因此,固晶设备需要具备高速度的生产能力,以提高生产效率并降低成本。3、良品率:先进封装的制造过程中,任何一个环节的失误都可能导致整个封装的失败。因此,固晶设备需要具备高良品率的生产能力,以确保封装的质量和可靠性。SiP是使用成熟的组装和互连技术,把各种集成电路器件集成到一个封装体内,实现整机系统的功能。北京模组封装测试

汽车电子里的 SiP 应用正在逐渐增加。北京模组封装测试

为了在 SiP 应用中得到一致的优异细间距印刷性能,锡膏的特性如锡粉尺寸、助焊剂系统、流变性、坍塌特性和钢网寿命都很重要,都需要被仔细考虑。合适的钢网技术、设计和厚度,配合印刷时使用好的板支撑系统对得到一致且优异的锡膏转印效率也是很关键的。回流曲线需要针对不同锡膏的特性进行合适的设计来达到空洞较小化。从目前的01005元件缩小到008004,甚至于下一代封装的0050025,锡膏的印刷性能变得非常关键。从使用 3 号粉或者 4 号粉的传统表面贴装锡膏印刷发展到更为复杂的使用 5、6 号粉甚至 7 号粉的 SiP 印刷工艺。新的工艺钢网开孔更小且钢网厚度更薄,对可接受的印刷锡膏体积的差异要求更为严格。除了必须要印刷更小和更薄的锡膏沉积,相邻焊盘的间隙也更小了。有些厂家已经开始尝试50 μm 的焊盘间隙。北京模组封装测试