商机详情 -

浙江电子元器件特种封装市价

CSP封装,CSP的全称为 Chip Scale Package,为芯片尺寸级封装的意思。它是BGA进一步微型化的产物,做到裸芯片尺寸有多大,封装尺寸就有多大。即封装后的IC尺寸边长不大于芯片长度的1.2倍,IC面积只比晶粒(Die)大不超过1.4倍。CSP封装可以让芯片面积与封装面积之比超过1:1.14,已经非常接近于1:1的理想情况。在相同的芯片面积下,CSP所能达到的引脚数明显地要比TSOP、BGA引脚数多得多。TSOP较多为304根引脚,BGA的引脚极限能达到600根,而CSP理论上可以达到1000根。由于如此高度集成的特性,芯片到引脚的距离较大程度上缩短了,线路的阻抗明显减小,信号的衰减和干扰大幅降低。CSP封装也非常薄,金属基板到散热体的有效散热路径只有0.2mm,提升了芯片的散热能力。SOP 封装主要用于低频、低功率的场合,如电子玩具、家电产品等。浙江电子元器件特种封装市价

贴片技术(SMT),这些SOT封装的芯片并不是像Wafer那样一盘几万颗,它的包装形式如图4-80(a)所示的载带(Tape)的方式包装,载带卷成圆盘如图4-80(b)所示。图4-80(b)所示的载带卷轴是SMT设备所接受的标准包装,类比于Wafer是纽豹TAL-15000所接受的标准包装一样。(a)封装载带图 (b)封装载带卷轴图,SMT是表面组装技术(表面贴装技术,Surface Mount Technology的缩写),是目前电子组装行业里流行的一种技术和工艺。一般采用SMT之后,电子产品体积缩小40%~60%,重量减轻60%~80%,且具有可靠性高、抗震能力强、高频特性好等特点。同时易于实现自动化,提高生产效率,降低成本。在超高频RFID应用中,较常使用的是电子器件生命周期管理和特种标签。可以回顾图4-25,只需要在电子产品的主板上合适的位置SMT上电子标签芯片,并在PCB板上设计天线即可。天津半导体芯片特种封装服务商不同的 MOS 管封装类型有各自的应用情况和优缺点。

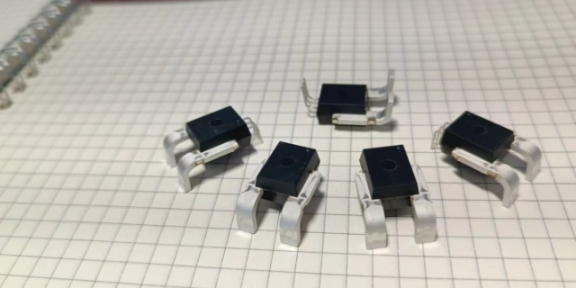

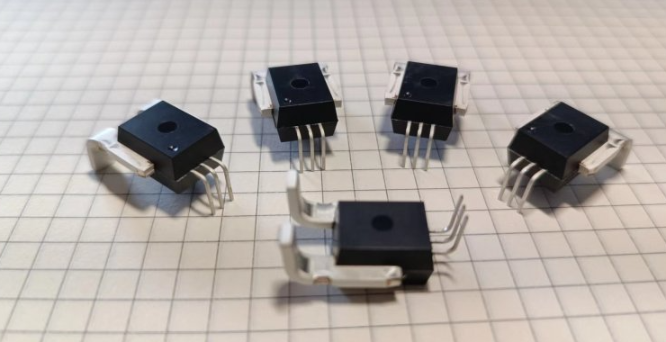

不同的 MOS 管封装类型有各自的应用情况和优缺点。不同的封装、不同的设计,MOS 管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样。因此,在选择 MOS 管时,封装是重要的参考因素之一。例如,对于需要高功率输出的电路,应该选择具有良好散热性能的封装,而对于需要高密度集成的电路,应该选择小型化的封装。设计者需要根据实际需求和电路板的安装要求来选择合适的封装类型,以确保 MOS 管在实际应用中发挥较佳性能。

自上世纪90年代以来,随着有机封装基板在更多I/O应用中取代铅框架和陶瓷封装,该市场持续增长,2011年达到约86亿美元的峰值,并在2016年开始稳步下滑,2016年只达到66亿美元。这种下降的部分原因是由于个人电脑和移动电话市场进入了成熟期,停滞不前的出货量和组件和集成封装降低了对先进封装包的需求。更重要的是向更小系统的全方面推进,这需要从更大的线结合PBGA到更小的FCCSP的转变。这减少了单位封装基板使用的面积,而且这种转变也要求每个基板具有更高的路阻密度,以允许更紧密的倒装芯片互连。封装基板的另一个重要的不利因素来自WLCSP的流行,尤其是在智能手机中。当较小的WLCSP取代引线框封装时,较大的WLCSP(包括扇出式WLCSP)取代了引线键合和倒装芯片CSP,从而消除了潜在的有机封装基板。SOT封装由一个塑料外壳和多个引脚组成,外形类似于一个透明的方形或圆形盒。

在选择芯片封装类型时,主要考虑以下几个方面的因素:1、封装体的尺寸。由于封装工艺的极限会限制芯片尺寸(长度、宽度和厚度),在选择封装体时,首先保证芯片能够安装进封装体,再根据产品厚度要求选择封装体厚度。随着消费类电子越来越朝轻、薄、短、小的方向发展,封装产品的厚度也越来越薄,选择封装体尺寸应优先选择小尺寸、薄型的封装体,以节约PCB的面积。2、封装体引脚数,所选择的封装体总引脚数应等于或大于集成电路芯片所需要的引出端总数(包括输人、输出、控制端、电源端、地线端等)。PGA 封装主要用于高频、高功率的场合,如通信设备、计算机显卡等。天津半导体芯片特种封装服务商

使用金属 TO 外壳封装可实现 25Gbit/s 以上传输速率。浙江电子元器件特种封装市价

由于QFN封装不像传统的SOIC与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电路径短,自感系数以及封装体内布线电阻很低,所以,它能提供突出的电性能。此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热的通道,用于释放封装内的热量。通常,将散热焊盘直接焊接在电路板上,并且PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。由于体积小、重量轻,加上杰出的电性能和热性能,这种封装特别适合任何一个对尺寸、重量和性能都有要求的应用。浙江电子元器件特种封装市价